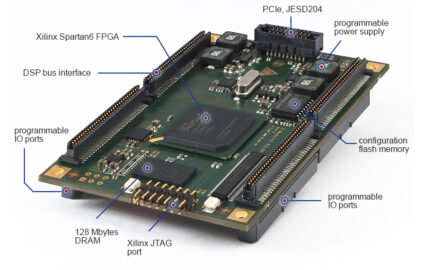

Xilinx Spartan6 XC6SLX45T FPGA (optional LX100T)

DSP Interface:

32-bit D.Module2 Bus Interface

One Gigabit Transceiver (SRIO)

Two Synchronous Serial Ports

I²C

D.Module2 Expansion Port with 12 LVDS-pairs / 24 single-ended signals

access to the FPGA Configuration

Flash for in-system updates

User-I/O: up to 49 LVDS-pairs / 98 single-ended signals

programmable I/O voltage 1.8, 2.5, or 3.3V

3 Gigabit Transceivers (PCI/e, JESD204/A, SGMII, SATA, SRIO)

FMC LPC signal standard compatible

128M bytes local DDR3 memory

3.3V single-supply